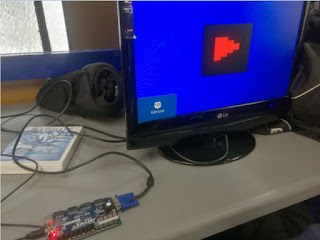

Laboratorio 8 # VGA

Implementación en código VHDL para visualizar una imagen en un monitor a través del puerto VGA de la FPGA.El código VHDL requiere un contador Horizontal y Uno Vertical, para poder llevar el electrón por el camino que pintara en la pantalla. Para desarrollar cada una de las imagines se utilizará la memoria ROM que será llena con los datos a mostrar. se implementaron 25 memorias ROM visualización VGA pantalla ROM imagen a visualizar